JETIR.ORG

# ISSN: 2349-5162 | ESTD Year : 2014 | Monthly Issue

# **JOURNAL OF EMERGING TECHNOLOGIES AND** INNOVATIVE RESEARCH (JETIR)

An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# **Implementation of 9 Stage Low Power Current Starved Ring VCO**

### Angad Kumar<sup>1</sup>

Department of Electronics and Communication Engineering Institute of Engineering and Technology Dr. Ram Manohar Lohia Avadh University Ayodhya, India Email: angad.knit@gmail.com

#### Prof. Ramapati Mishra<sup>2</sup>

Department of Electronics and Communication Engineering Institute of Engineering and Technology Ayodhya, India Email: director.rpm@gmail.com

### Dr. Shiksha Jain<sup>3</sup>

Asst. Prof, Department of Electronics and Communication Engineering Institute of Engineering and Technology Ayodhya, India Email: shiksha98jain@gmail.com

#### Er. Abhishek Srivastava<sup>4</sup>

Asst. Prof, Department of Electronics and **Communication Engineering** Institute of Engineering and Technology Dr.Ram Manohar Lohia Avadh University Dr.Ram Manohar Lohia Avadh University Dr.Ram Manohar Lohia Avadh University Ayodhya, India

Email: abhishek200959@gmail.com

Abstract: This project aims to construct a low-power (2.75mw) radio frequency (1.8GHz) Phase Locked Loop (PLL) with a 0.18-µm CMOS era. Current Starved VCO and Differential Pair VCO evaluations have been completed and studied for low and high frequency evaluations, respectively. Spice in the 0.18-µm period created and simulated each aspect of PLL in the Tanner EDA. Both previous designs were simulated in the same environment, and the effects of two maximum critical VLSI restrictions, Speed (High frequency range) and Power intake, were examined. The Differential VCO's fast speed and locking overall performance has been compared to the lower energy consumption benefit of Current starved mainly based VCOs.

Keywords: Charge pump, Current Starved VCO, PLL, Phase noise and VCO.

## I. INTRODUCTION

Optical phase locked loops (OPLLs) are expected to have a huge range of programs in diverse light wave networks specifically inside the subject of coherent optical communication, likewise the utility of PLL at radio frequencies. One software of OPLL is the synchronisation of laser frequencies in multi wavelength networks and another utility is the development of homodyne receivers. It affords a doubtlessly handy method of generating channel offsets in a dense wavelength division multiplexing system. It can also be used as a segment or frequency demodulator. However, the optical phase locking approaches are extra successfully applied in building optical homodyne and heterodyne receivers. The overall performance of an OPLL depends on various noise assets and loop put off time like an everyday

digital or electric phase locked loop. These also restrict the stableness of the loop.

A section locked loop (PLL) is comments manage system in which the phase of a signal is locked by controlling the immediate frequency of the VCO. The control signal is derived from low pass filtering of the output of a phase identifier that compares the instant segment of the nearby oscillator output and the input. Closed-loop frequency manipulate machine's functioning is primarily based on the section sensitive detection of segment and/or Frequency difference among the reference and output indicators of the transceiver block. Segment-locked loops (PLL) consist of Voltage Controlled Oscillator (VCO) that is the quintessential part of the frequency generators and clock healing circuits. PLL circuits had been used to demodulate FM signals for the long time, making out of date to the Foster-Seeley and radio frequency demodulators of the earlier times. A VCO unearths style of packages and consequently effects in distinctive architectural designs which includes LC oscillator, Resonator circuit (the usage of Ring structure), Relaxation Oscillator and so forth. Due to higher velocity and higher stability in output oscillations, the differential amplifier based ring oscillator is used primarily with narrow variety of degrees which results in small power intake [1]. This essential feature of the differential amplifier based configuration has motivated this painting to stay focused round it. Further lesser power dissipation can be received the usage of a few different configurations which includes Partial +ve Feedback gadget and Ring Oscillator structure [2]. LC circuit based tuned oscillators have proved their superiority for the high frequency (MW band) packages, but the gain expenses due to highly complex circuit, because of inductors [3]; while a hoop structure has

an advantage of smaller area compared to the LC oscillator. Ring oscillator shows an added benefit of huge tuning range additionally [4]. Since previous several researches published whose system output vary of their frequency of operation, range of tuning, section noise features, strength consumption, circuit structure and stage of synthesis. Plenty of researches had been conducted in knowing a high lock variety PLL with smaller lock time and electricity. There had been papers on Mixed /Hybrid Signal Analysis and Low energy design the usage of technology starting from 600-nm to 22-nm. In this paintings, the design specification for 180 nm generation has been selected for having lesser excessive order outcomes and accomplishing higher Signal-to-Noise (S/N) ratio. The paper presents the layout of 1.8 GHz 2.75 mW PLL simulated with 0.18-µm CMOS generation in IC-Station (Mentor Graphics) on Eldo-Net simulator. Emerging from single degree oscillator, the PLL uses various circuit structures to achieve excessive tunable frequency variety with low energy dissipation. The essential purpose of the paper is to layout and perform the comparative evaluation on two one of a kind VCO layout's issue which can be Current Starved VCO (CSVCO) and Differential Pair VCO (DAVCO) on the idea of tunable frequency variety (velocity), Power dissipation, monitoring variety and performance.

#### II. METHODOLOGY

With reverse frame bias generation a superior performance low Voltage Control Ring Oscillator turned into proposed by means of Milind Gautam et al. The work highlights the designing of voltage managed ring system oscillator circuit. It is used in the discipline of critical conversation structures with excessive frequency of oscillation. The circuit designed shows effective end result with lesser leakage inside the circuit. A new method for decreasing the power intake using substrate biasing method is provided. It additionally gives an description of CMOS Ring Oscillators for frequency and amplitude. Firstly, Voltage Controlled Oscillator (VCO) is investigated to accurate electricity dissipation and leakage present day. It is utilized in verbal exchange machine and this circuit has to be sufficient to machine designers [7]. In Ring Oscillator, amplitude and frequency are both sufficient for massive signal however a sinusoidal waveform is unknown. It is used for calculating the leakage and the energy. In the VCO, the exceptional of communication link and the most vital issue this is the linearity are tested however at a low price. The first demand of advanced VLSI era is low power intake. Nidhi Thakur et al explained a low energy design, which determined that, it relies upon on Threshold Voltage of transistor and the supply input voltage. This is normally useful; due to the fact threshold voltage and supply voltages can be managed without problems. The circuit is in addition designed successfully which will make it perform in higher pace with lower strength requirement inside the circuit. Thus with the aid of doing so effective care must be taken for designing of the circuit else exchange off will have an effect on the layout.

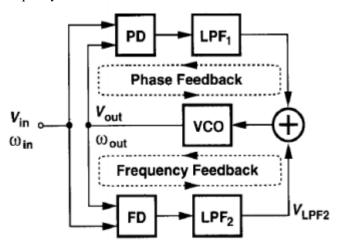

PLL is a comments machine that maintains the input signal aligned, w.r.t reference signal. There are several structures of PLL. Here we pick to put into effect Charge-Pump based PLL as kind I PLLs have tight alternate-offs (among  $\omega_{LP}$  F and  $\zeta$ , the damping ratio) and feature limited acquisition variety. In order to remedy the purchase hassle, frequency comparison is likewise achieved similarly to the section detection, [2, 4] as proven in Fig 1. For the periodic alerts it's possible to combine both, frequency and phase section

feedback loops and the developed new structure is Phase Frequency Detector.

Fig 1: Block Diagram of Phase and Frequency Detector (PFD)

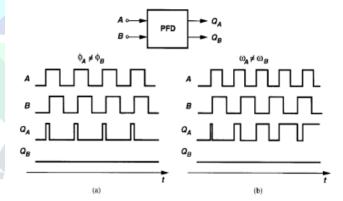

The operation of PFD may be without problems understood from Fig 2. Lets expect  $Q_A$  and  $Q_B$  are zero to start with. Thus while input A rises (before enter B), this results in  $Q_A$  being high however  $Q_B$  nonetheless low. The circuit will continue to be on this state till B rises, at which factor  $Q_A$  will go back to 0 and  $Q_B$  will nevertheless be zero. Similar is going for  $Q_B$  and  $Q_A$  while enter B rises earlier than input A. It can be without difficulty determined that during Fig 2 (a)  $Q_A$  represents the phase difference  $(\phi_A$  -  $\phi_B)$  between the inputs while in Fig 2 (b)  $Q_A$  represents the frequency variant  $(\omega_A$  -  $\omega_B)$  between the inputs.

Fig2: Operation of Phase and Frequency Detector (PFD)

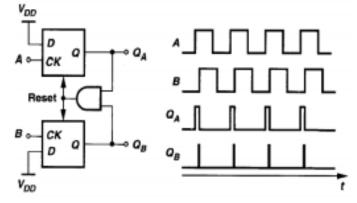

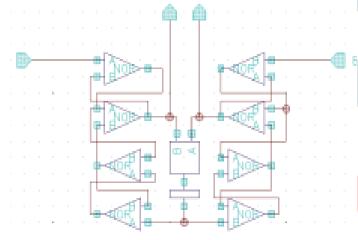

Phase and Frequency Detector can be incorporated as shown in Fig 3 i.e. two edge triggered resettable D flip flops with their D inputs tied to logic 1.

Fig3: Implementation of Phase and Frequency Detector (PFD)

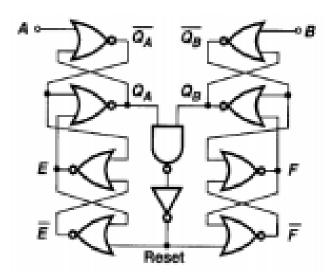

Fig 4: Phase and Frequency Detector at Gate Level

Fig 5: PFD Realisation

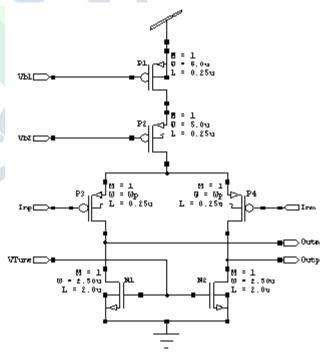

Fig 6: Schematic Design of Proposed Differential Pair Based Ring VCO.

There are a few problems associated with this architecture. A good way to acquire the wide tuning variety is by the use of a single tail current, the tuning variety is restrained by the manipulating voltage range. The manage voltage is normally constraint via the electricity deliver voltage, i.e.  $0 \le V_{control} \le V_{dd}$ , where  $V_{dd}$  is the supply voltage, a constraint related to the layout era. If we select the small tail modernday, the tail modern remains no longer huge sufficient even that the manipulating voltage reach the up restriction in order that the excessive quit frequency range of VCO is small. On the opposite hand, if we pick out the massive tail

present day, the tail present day is still big even that the manage voltage reached the decrease limit in order that the lower give up frequency range of VCO is large [8].

#### III. RESULTS AND DISCUSSION

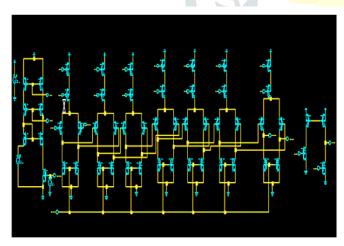

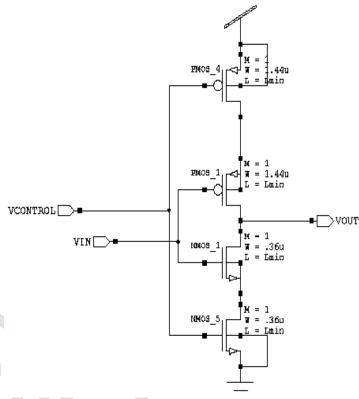

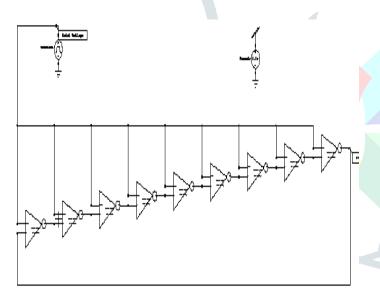

Fig 7 shows the 9 stage of CS VCO schematic diagram, Fig 8 shows the cell diagram of 9 stages CS VCO and Fig 9 shows the simulation result of 9 stage of CS VCO.

Fig 7: Schematic Diagram 9 Stage of CS VCO

Fig 8: Cell Diagram of 9 Stage of CS VCO

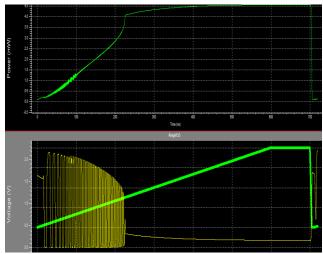

Fig 9: Simulation Result of 9 stage of CS VCO

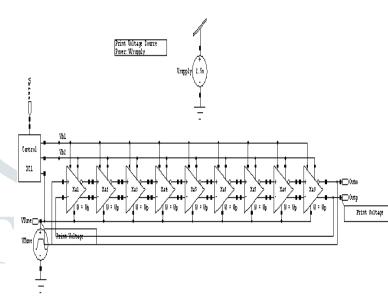

Fig 10 shows the 9 stage of DA VCO schematic diagram, Fig 11 shows the cell diagram of 9 stages DA VCO and Fig 12 shows the simulation result of 9 stage of DA VCO.

Fig 11: Cell Diagram of 9 stage of DA VCO

Fig 10: Schematic Diagram 9 Stage of DA VCO

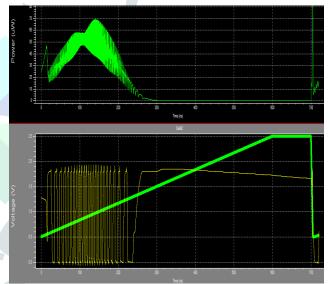

Fig 12: Simulation Result of 9 stage of DA VCO

#### IV. CONCLUSION

The comparison and execution of two VCO designs are discussed in this work. The current starved ring outperforms the differential pair VCO in terms of low power consumption and broad frequency range, whereas the differential pair VCO is preferred for its high frequency and wide frequency range. The developed PLL with current starved VCO consumes 1.169 mW power from a 1.3 V supply and has a shorter lock time, according to the research 6.22 mw is consumed by PLL with differential VCO. In the frequency range of 740 MHz to 1.72 GHz, the differential VCO curve is linear, So the centre frequency is around 1 GHz, and it has a wide adjustable range. As a result, the Differential architecture for VCO appears to be a better choice for speed and linearity, especially for quick communication devices, although the demanding necessity for lower power consumption for remote wireless circuits still favours the Current starved VCO. With the enhanced

Charge Pump design, steady and high frequency outputs with very low phase noise may be obtained. Also, by properly sized Divider network transistors and using them in a Master Slave arrangement, the power might be greatly lowered.

#### REFERENCES

- [1] Suraj Kumar Saw, Vijay Nath, "An Ultra Low Power And Low Phase Noise Current Starved CMOS VCO For Wireless Application", 2015 Interational Conference on Industrial Instrumentation and Control (ICIC) College of Engineering Pune, India May28-30, 2015

- [2] Romesh Kumar Nandwana "A Calibration-Free Fractional-N Ring PLL Using Hybrid Phase/Current-Mode Phase Interpolation Method", IEEE journal of solid-state circuits, vol. 50, no. 4, April 2015

- [3] Shruti Suman, K. G. Sharma, P. K. Ghosh, "Design Of PLL Using Improved Performance Ring VCO", International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT) 2016

- [4] Javier Agustin, "Efficient Mitigation of SET Induced Harmonic Errors in Ring Oscillators", IEEE transactions on nuclear science, vol. 62, no. 6, December 2015

- [5] Wei Deng, Dongsheng Yang, Tomohiro Ueno, "A Fully Synthesizable All-Digital PLL With Interpolative Phase Coupled Oscillator, Current-Output DAC, and Fine-Resolution Digital Varactor Using Gated Edge Injection Technique", IEEE journal of solid-state circuits, vol. 50, no. 1, January 2015

- [6] J.Naga Raju, K.Naveen, CH.Sreenu, "CMOS Voltage Controlled Oscillator (VCO) Design with Minimum Transistors", ©2016 IJRTI | Volume 1, Issue 3 December 2016 | ISSN: 2456-3315

- [7] A. C. Demartinos, A. Tsimpos, S. Vlassis, G. Souliotis, Delay Elements Suitable for CMOS Ring Oscillators, Journal of Engineering Science and Technology Review 9 (4) (2016) 98 101.

- [8] Rafiul Islam, Ahmad Nafis Khan Suprotik, Md.Tawfiq Amin, "Design and analysis of 3 stage ring oscillator based on MOS capacitance for wireless applications" 2017 International Conference on Electrical, Computer and Communication Engineering (ECCE).

- [9] Jingdong DENG, "Digital Phase Locked Loop For Low Utter Applications" United States Patent Application Publication, 15 July 2016.

- [10] J. Jalil, M. B. I. Reaz1, M. A. M. Ali1, T. G. Chang, "A Low Power 3-Stage Voltage-Controlled Ring Oscillator in 0.18  $\mu$ m CMOS Process for Active RFID Transponder", elektronika ir elektrotechnika, ISSN 1392-1215, vol. 19, no. 8, 2013

- [11] Muhammad Faisal, David D. Wentzloff, "An Automatically Placed-and-Routed ADPLL for the Med Radio Band using PWM to Enhance DCO Resolution", 978-1-4673-6062-3/13/\$31.00 © 2013 IEEE

- [12] Skyler Weaver, "Digitally Synthesized Stochastic Flash ADC Using Only Standard Digital Cells", IEEE transactions on circuits and systems-I: regular papers, vol. 61, no. 1, January 2014

- [13] Wei Deng, Dongsheng Yang, Tomohiro Ueno, Teerachot Siriburanon, Satoshi Kondo, Kenichi Okada, and Akira Matsuzawa, "A 0.0066mm2 780mW Fully Synthesizable PLL with a Current Output DAC and an Interpolative Phase-Coupled Oscillator using Edge Injection Technique" © 2014 IEEE International Solid-State Circuits Conference.